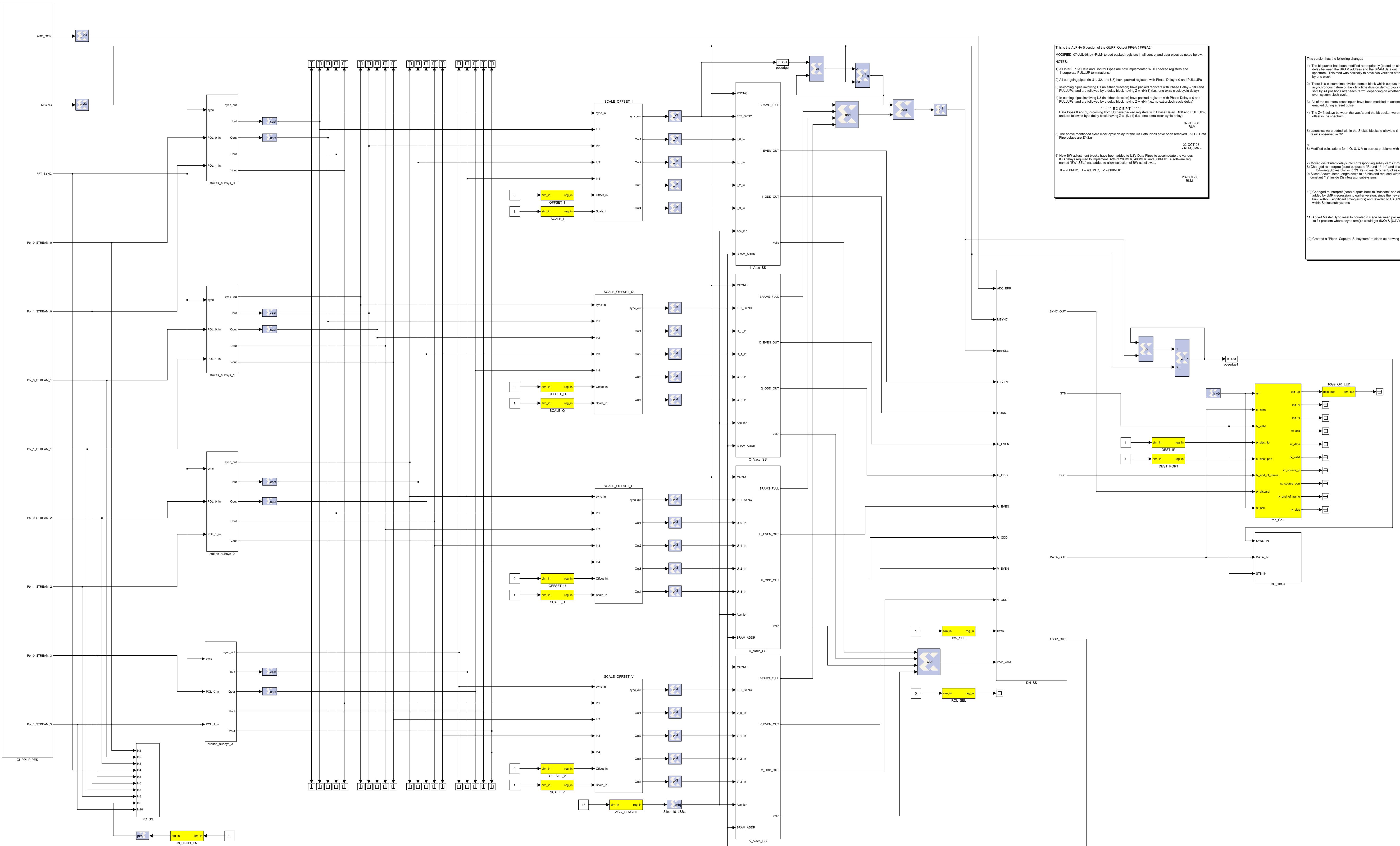

This is the ALPHA 0 version of the GUPP Output FPGA (FPGA2)

MODIFIED: 07-JUL-08 by -RLM- to add packed registers in all control and data pipes as noted below...

NOTES:

1) All Inter-FPGA Data and Control Pipes are now implemented WITH packed registers and incorporate PULLUP terminations.

2) All out-going pipes (in U1, U2, and U3) have packed registers with Phase Delay = 0 and PULLUPs

3) In-coming pipes involving U (in either direction) have packed registers with Phase Delay = 180 and PULLUPs, and are followed by a delay block having  $Z = 4N + 1$  (i.e., one extra clock cycle delay)

4) Inter-FPGA pipes involving U (in either direction) have packed registers with Phase Delay = 0 and PULLUPs, and are followed by a delay block having  $Z = 4N + 1$  (i.e., one extra clock cycle delay)

\*\*\*\*\* X C E P T \*\*\*\*\*

Data Pipe 0 and 1, in-coming from U3 have packed registers with Phase Delay = 180 and PULLUPs, and are followed by a delay block having  $Z = 4N + 1$  (i.e., one extra clock cycle delay)

07-JUL-08 -RLM-

5) The above mentioned extra clock cycle delay for the U3 Data Pipes have been removed.

22-OCT-08 -RLM\_JMR-

6) New BW adjustment blocks have been added to U3's Data Pipes to accomodate the various U3 BW requirements. The BW adjustment blocks are located in the 200MHz, 400MHz, and 800MHz. A software reg. named **BW\_SEL** was added to allow selection of BW as follows:

0 = 200MHz, 1 = 400MHz, 2 = 800MHz

23-OCT-08 -RLM-

This version has the following changes:

1) The bit packer has been modified appropriately (fixed in simulation) to accomodate a one clock delay between the bit packer and the BRAM data out. This was causing a 4-bit error in the spectrum. This mod was basically to have two versions of the address counter, one version delayed by one clock.

2) The custom time division demux block which outputs the data in the order required. The asynchronous nature of the xilinx time division demux block was causing the bins to intermittently shift by 4 positions after each "arm" (i.e., one extra clock cycle delay)

3) All of the counters' reset inputs have been modified to accomodate the requirement that they be enabled during a reset pulse.

4) The Z=3 delays between the vec's and the bit packer were removed. They were causing a 16-bit offset in the spectrum.

5) Latencies were added within the Stokes blocks to alleviate timing errors and possibly fix erratic results observed in "V"

14-AUG-08 -RLM-

6) Modified calculations for I, Q, U, & V to correct problems with U & V

7) Moved destination delay to corresponding latencies throughout

8) Change in interest latency outputs to "round" IP and data pipe

9) Stated Average Throughput down to 30 Gb/s and reduced width of corresponding constraint "16" from Downstream subsystems

20-AUG-08 -RLM-

10) Changed to interpret (cast) outputs back to "truncate" and eliminated latencies added by JMR. Regressed to earlier version, since the newer version wouldn't boot with the signature timing errors and reverted to CASPER Power blocks within Stokes subsystems.

26-SEP-08 -RLM-

11) Added Master Sync reset to counter in stage between packer and 10Gb manager to fix problems where sync smd's would get ISM'd & UV's streams interchanged.

29-OCT-08 -RLM-

12) Created a "Pipes\_Capture\_Subsystem" to clean up drawing

29-OCT-08 -RLM-