davids5 opened a new pull request #3167: URL: https://github.com/apache/incubator-nuttx/pull/3167

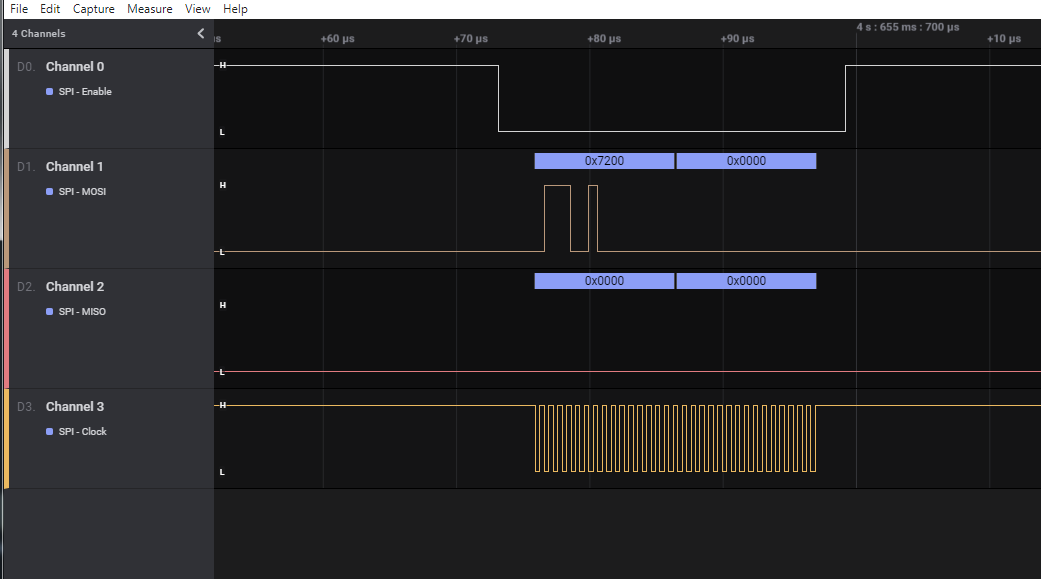

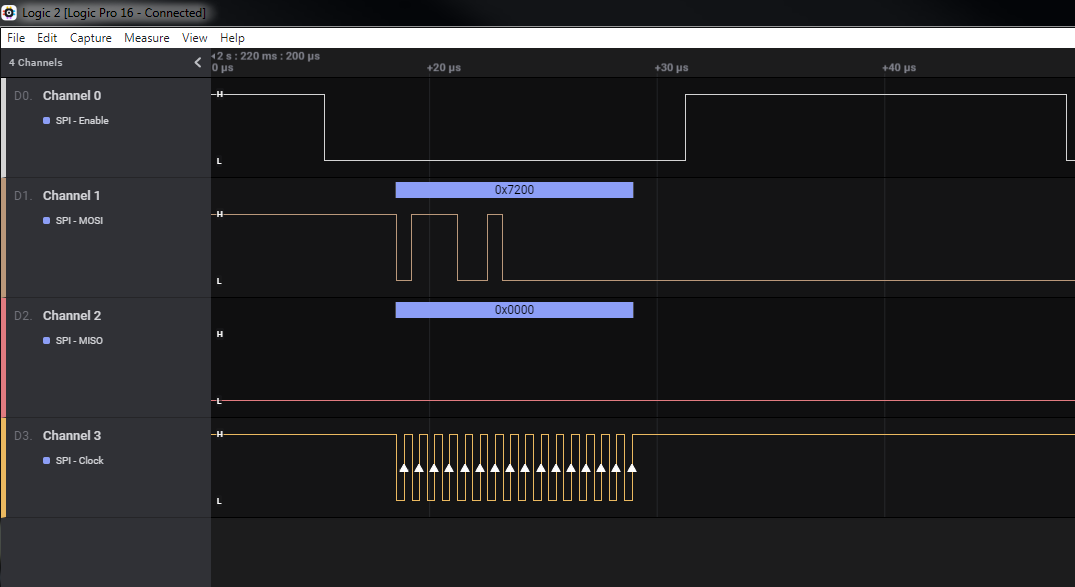

## Summary The STM32H7 SPI driver was not using the HW correctly. Albeit the manual is super confusing, the bottom line is this. That a memory access of 8, 16 and 32 bits, will write 1 byte, 2 bytes or 4 bytes to the FIFIO. With a frame size of 16 (CFG1_DSIZE == 0xf) a 32 bit write to SPI_TXDR will place 2 16 bit values into the FIFO. So the date sent on the wire was the correct first 16 bit word followed by an incorrect 16 bit word of 0x0000. This can be observed on master with an STM32H7 in the first image. I believe the STM32F7 (and all SoC's sharing the same IP) have the same issues but that is TBD. ## Impact Master on STM32H7 note the 32 clocks on a 16 bit transfer.  After on STM32H7 as expected 16 bits and 16 clock edges.  ## Testing PX4 cuav_x7pro with ADIS16470 -- This is an automated message from the Apache Git Service. To respond to the message, please log on to GitHub and use the URL above to go to the specific comment. For queries about this service, please contact Infrastructure at: [email protected]